随着科技的飞速发展,全球半导体市场经历了从PC时代到智能手机时代,再到高性能计算(HPC)时代的三次主要增长驱动力的转变。据World Semiconductor Trade Statistics数据显示,HPC正引领全球半导体市场规模迈向新高度,预计从2023年的5150亿美元增长至2028年的8000亿美元,复合年均增长率(CAGR)高达9.2%。在这一背景下,基于SerDes的Chip-to-Chip技术成为提升数据中心算力协同效率的关键,使得HPC集群能够实现前所未有的超大规模组网。

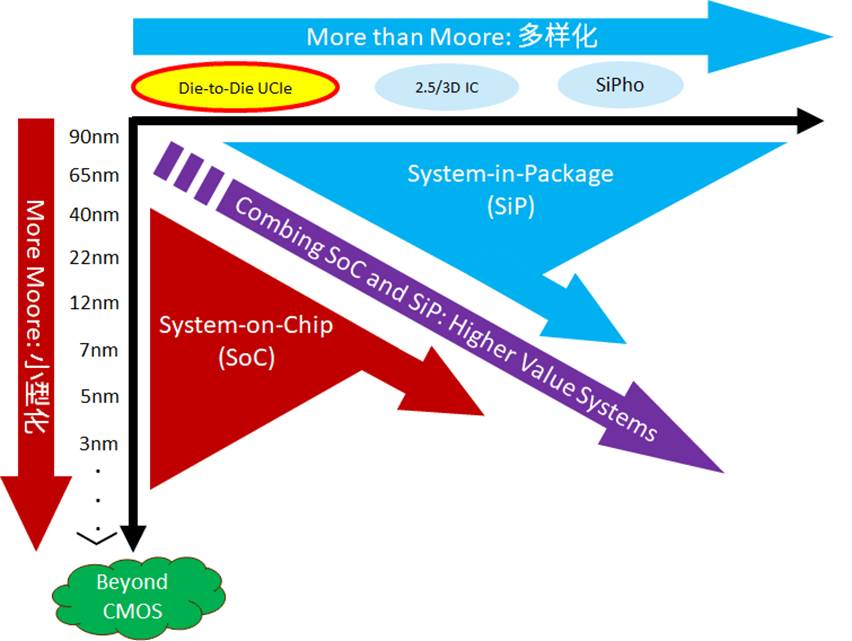

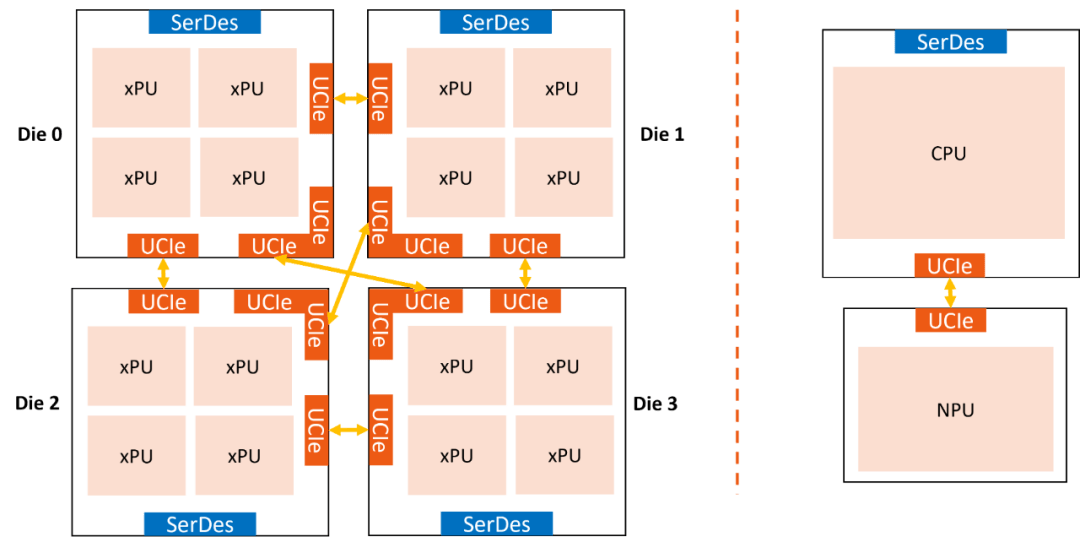

在HPC领域,UCIe与SerDes技术的结合为大算力芯片带来了革命性的变化。UCIe作为统一的接口标准,打破了Foundry和工艺之间的壁垒,使得不同Chiplet之间的互联成为可能,进一步优化了封装成本和效率。这一技术不仅推动了Chiplet向市场化迈进,还成为国内外HPC芯片设计的主流选择。晟联科作为国内领先的高速接口IP供应商,其16G/32G UCIe IP解决方案以低延时、低功耗和高性能的特点,在HPC、数据中心、CPU及加速器等应用场景中发挥了重要作用。

晟联科的UCIe+SerDes高速IP解决方案在提升HPC芯片性能方面表现尤为突出。首先,它提供了高带宽的数据传输能力,使得海量数据能够在芯片内部及芯片间快速流通,满足了人工智能和高性能计算领域对高速数据传输的迫切需求。其次,通过优化信号传输路径、减少信号失真及采用高效的时钟同步机制,UCIe+SerDes技术实现了低延时,为实时数据处理和大参数模型训练提供了坚实的技术支撑。最后,Multi-Die设计不仅提升了良率,还使得不同Die可以灵活配置成不同的产品系列,进一步降低了成本,加快了产品上市速度。

为了应对HPC等大算力应用带来的挑战,晟联科推出了112G SerDes与光模块配合实现的Chip-to-Chip高速互连方案。这一方案让分布式运行的多Die集成为一颗高性能运行的芯片,实现了低延时、高速度的数据传输。同时,该方案支持同构和异构集成HPC芯片架构,提供了优秀的产品性能表现。

晟联科的UCIe+SerDes高速IP互连解决方案经过多年的研发和积累,已成为国内少数在先进工艺下同时支持32G UCIe和112G SerDes的高速接口IP解决方案的公司。该方案不仅实现了高速、低延时和长距离传输,还助力HPC高性能计算客户取得了更大的创新。目前,晟联科的高速SerDes IP已有超过2亿条通道在全球500强客户的芯片和设备中出货,证明了其技术的可靠性和市场认可度。

晟联科作为全球高速接口IP领域的佼佼者,始终致力于为客户提供专业、高效的技术支持和服务。其上海总部和研发中心汇聚了众多行业精英,深圳、武汉等地的办事处则为客户提供及时、周到的本地化服务。晟联科还拥有20多项发明专利,为客户的技术和应用场景提供了强有力的支持。未来,随着技术的不断进步和市场的持续发展,相信晟联科将继续在高速接口IP领域发挥引领作用,为加速算力提供更为卓越的解决方案。